# Snapdragon 845 HDK Hardware Development Kit User Guide

Your use of this document is subject to and governed by those terms and conditions in the LICENSE AND PURCHASE TERMS AND CONDITIONS FOR INTRINSYC DEVELOPMENT PLATFORM KITS, which you or the legal entity you represent, as the case may be, accepted and agreed to when purchasing a Development Kit from Intrinsyc Technologies Corporation ("Agreement"). You may use this document, which shall be considered part of the defined term "Documentation" for purposes of the Agreement, solely in support of your permitted use of the Development Kit under the Agreement. Distribution of this document is strictly prohibited without the express written permission of Intrinsyc Technologies Corporation and its respective licensors, which they can withhold, condition or delay in its sole discretion.

Lantronix is a trademark of Lantronix, Inc., registered in the United States and other countries. Intrinsyc is a trademark of Intrinsyc Technologies Corporation, registered in Canada and other countries.

Qualcomm® is a trademark of Qualcomm® Incorporated, registered in the United States and other countries. Other product and brand names used herein may be trademarks or registered trademarks of their respective owners.

This document contains technical data that may be subject to U.S. and international export, re-export, or transfer ("export") laws. Diversion contrary to U.S. and international law is strictly prohibited.

© 2020 Lantronix, Inc. All rights reserved.

#### **Contacts**

#### Lantronix, Inc.

7535 Irvine Center Drive, Suite 100 Irvine, CA 92618, USA

Toll Free: 800-526-8766 Phone: 949-453-3990 Fax: 949-453-3995

# IES Customer Support Portal

https://helpdesk.intrinsyc.com

Lantronix Technical Support http://www.lantronix.com/support

#### **Sales Offices**

For a current list of our domestic and international sales offices, go to the Lantronix web site at <a href="http://www.lantronix.com/about-us/contact/">http://www.lantronix.com/about-us/contact/</a>

# **Revision History**

| Date         | Rev. |     | Comments                                                                      |

|--------------|------|-----|-------------------------------------------------------------------------------|

| May 2018     |      | 1.0 | Initial release. Intrinsyc document number: ITC-01IMP1335-UG-001              |

| October 2020 |      | А   | Version information, installation instructions and package contents clarified |

For the latest revision of this product document, please go to: <a href="http://tech.intrinsyc.com">http://tech.intrinsyc.com</a>.

# **Contents**

| 1 | Introd | luction                                   | 7  |

|---|--------|-------------------------------------------|----|

|   | 1.1 F  | Purpose                                   | 7  |

|   |        | Scope                                     |    |

|   |        | ntended Audience                          |    |

| 2 | Docui  | ments                                     | 8  |

|   | 2.1 A  | Applicable Documents                      | 8  |

|   |        | Reference Documents                       |    |

|   |        | Terms and Acronyms                        |    |

| 3 | Snapo  | dragon 845 Hardware Development Kit       | 10 |

|   | 3.1 I  | ntroduction                               | 10 |

|   | 3.2    | Development Platform Notice               |    |

|   | 3.3 A  | Anti-Static Handling Procedures           | 10 |

|   |        | Kit Contents                              |    |

|   | 3.5 H  | Hardware Identification Label             | 12 |

|   |        | System Block Diagram                      |    |

| 4 | Proce  | essor Board                               | 14 |

|   | 4.1 F  | Processor Board Mechanical Properties     | 15 |

|   | 4.2 H  | Hardware Specification                    | 15 |

| 5 | Carrie | er Board                                  | 18 |

|   | 5.1    | Dip switch Configuration Options          | 19 |

|   |        | HDK845 Carrier Board Expansion Connectors |    |

|   |        | Power Option                              |    |

|   | 5.2.2  | Debug Serial UART header J2103            |    |

|   | 5.2.3  | B Debug Serial UART over USB J2102        | 25 |

|   | 5.2.4  | 4 JTAG header J2101                       | 25 |

|   |        | Sensor IO Expansion Header J2501          | 27 |

|   | 5.2.6  | NFC Expansion Header J2401                | 28 |

|   | 5.2.7  | 7 Headset Jack J1501                      | 29 |

|   | 5.2.8  | 3 Audio Inputs Expansion Header J1601     | 30 |

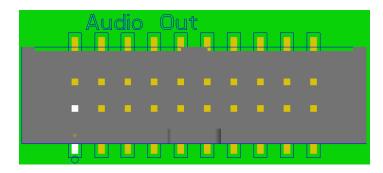

|   | 5.2.9  | Audio Outputs Expansion Header J1602      | 31 |

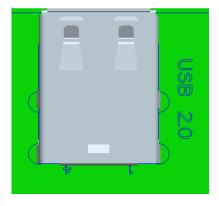

|   | 5.2.1  | 10 USB TYPE A Connector J1101             | 32 |

|   | 5.2.1  | 11 USB3.1 Type C Connector J1201          | 33 |

|   | 5.2.1  |                                           |    |

|   | 5.2.1  |                                           |    |

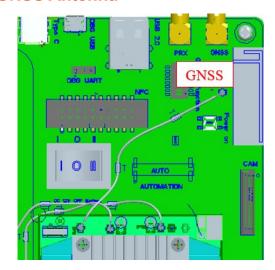

|   | 5.2.1  | 14 GNSS SMA Connector J3802               | 34 |

|   | 5.2.1  |                                           |    |

|   | 5.2.   | 16 Vertigo Sensor connector               | 38 |

|   | 5.2.   | 17 HDMI Connector                         | 39 |

| 5.2.19 WiGig Antenna Module                                                                    | 40 |

|------------------------------------------------------------------------------------------------|----|

| 6 Display Card                                                                                 | 41 |

| 6.1 HDK845 Display Card Overview                                                               | 41 |

| 6.2 Display Card Connector J0501                                                               |    |

| 6.3 LCD panel                                                                                  | 44 |

|                                                                                                |    |

| ist of Figures                                                                                 |    |

| Figure 4-1 HDK Processor Board                                                                 | 14 |

| Figure 5-1 HDK Carrier Board                                                                   | 18 |

| Figure 5-2 J0701 12V DC Power Jack                                                             | 24 |

| Figure 5-3 J2103 3.3V TTL Debug UART                                                           |    |

| Figure 5-4 J2102 Debug UART over USB                                                           |    |

| Figure 5-5 J2101 JTAG header                                                                   |    |

| Figure 5-6 J2501 Sensor Expansion Header                                                       |    |

| Figure 5-7 J2401 NFC Expansion Header                                                          |    |

| Figure 5-8 Headphone Jack                                                                      |    |

| Figure 5-9 J1601 Audio Inputs Expansion HeaderFigure 5-10 J1602 Audio Outputs Expansion Header |    |

| Figure 5-11 J1101 USB2.0 Type A Connector                                                      |    |

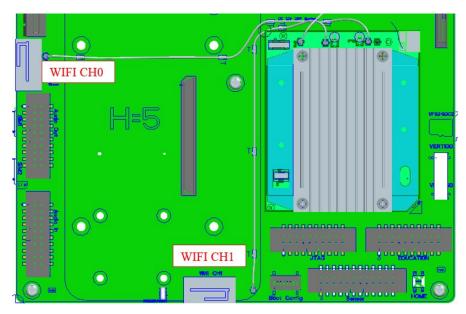

| Figure 5-12 On Board PCB WLAN Antennas                                                         |    |

| Figure 5-13 GNSS On Board PCB GNSS Antennas                                                    |    |

| Figure 5-14 GNSS SMA Connector                                                                 |    |

| Figure 5-15 Camera Connector (J1701)                                                           |    |

| Figure 5-16 Vertigo Connector (J1701)                                                          | 39 |

| Figure 5-17 HDMI Connector (J1401                                                              | 39 |

| Figure 5-18 Dip Switch S2301-8                                                                 | 39 |

| Figure 5-19 PCIe 1X Slot (J2701)                                                               | 40 |

| Figure 5-20 WiGig Antenna Module                                                               | 40 |

| Figure 6-1 HDK Display Card                                                                    |    |

| Figure 6-2 Display Card Default Configuration                                                  | 43 |

| ist of Tables                                                                                  |    |

|                                                                                                |    |

| Table 4-1 HDK845 Processor Board Mechanical Properties                                         |    |

| Table 5-1 HDK945 Carrier Reard Machanical Properties                                           |    |

| Table 5-1 HDK845 Carrier Board Mechanical Properties                                           |    |

| Table 5-2 Dip Switch S2301 HW / SW Configuration                                               |    |

| Table 5-3 Dip Switch S2302 HW / SW configuration                                               |    |

| Table 5-4 Carrier Board Expansion options and their usage                                      |    |

| Table 3-0 Debug OART Headel 02 100 Fill-Out                                                    | 20 |

5.2.18 PCI Express 1X Slot (Reserve)

\_40

| Table 5-6 JTAG Header J2101 Pin out                     | 26 |

|---------------------------------------------------------|----|

| Table 5-7 Sensor Expansion Header J2501 Pin out         | 27 |

| Table 5-8 NFC Expansion Header J2401 pin out            | 29 |

| Table 5-9 Audio Inputs Expansion Header J1601 Pin out   | 30 |

| Table 5-10 Audio Outputs Expansion Header J1602 Pin out | 31 |

| Table 5-11 GNSS Antenna Option                          | 34 |

| Table 5-12 MIPI CSI Camera Connector Pinouts (J1701)    | 35 |

| Table 5-13 MIPI CSI Camera Use Cases                    | 38 |

| Table 6-1 HDK845 Display Card Mechanical Properties     | 41 |

| Table 6-2 Display Power Domains                         | 43 |

# 1 Introduction

### 1.1 Purpose

The purpose of this user guide is to provide primary technical information on the Snapdragon 845 HDK Hardware Development Kit User Guide.

For more background information on this development kit, visit: www.lantronix.com

### 1.2 Scope

This document will cover the following items on the Snapdragon 845 Har:

- Block Diagram and Overview

- Hardware Features

- Configuration

- Processor board

- Carrier Board

- Display Board for LCD (Optional)

#### 1.3 Intended Audience

This document is intended for users who would like to develop custom applications on the Snapdragon 845 Hardware Development Kit.

# 2 Documents

This section lists the supplementary documents for the Snapdragon Q 845 Hardware Development Kit.

# 2.1 Applicable Documents

| Reference | Title                                                                                |

|-----------|--------------------------------------------------------------------------------------|

| A-1       | Intrinsyc Purchase and Software License Agreement for the Snapdragon Development Kit |

### 2.2 Reference Documents

| Reference | Title |

|-----------|-------|

|           |       |

# 2.3 Terms and Acronyms

| Term and acronyms | Definition                                                                             |

|-------------------|----------------------------------------------------------------------------------------|

| AMIC              | Analog Microphone                                                                      |

| ANC               | Audio Noise Cancellation                                                               |

| B2B               | Board to Board                                                                         |

| BLSP              | Bus access manager Low Speed Peripheral (Serial interfaces like UART / SPI / I2C/ UIM) |

| BT LE             | Bluetooth Low Energy                                                                   |

| CSI               | Camera Serial Interface                                                                |

| DSI               | MIPI Display Serial Interface                                                          |

| EEPROM            | Electrically Erasable Programmable Read only memory                                    |

| eMMC              | Embedded Multimedia Card                                                               |

| FCC               | US Federal Communications Commission                                                   |

| FWVGA             | Full Wide Video Graphics Array                                                         |

| GPS               | Global Positioning system                                                              |

| HDMI              | High Definition Media Interface                                                        |

| HSIC              | High Speed Inter Connect Bus                                                           |

| Term and acronyms | Definition                                                                                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|

| JTAG              | Joint Test Action Group                                                                                               |

| LNA               | Low Noise Amplifier                                                                                                   |

| MIPI              | Mobile Industry processor interface                                                                                   |

| MPP               | Multi-Purpose Pin                                                                                                     |

| NFC               | Near Field Communication                                                                                              |

| RF                | Radio Frequency                                                                                                       |

| SATA              | Serial ATA                                                                                                            |

| SLIMBUS           | Serial Low-power Inter-chip Media Bus                                                                                 |

| SPMI              | System Power Management Interface (Qualcomm® PMIC / baseband proprietary protocol)                                    |

| SSBI              | Single wire serial bus interface (Qualcomm® proprietary mostly PMIC / Companion chip and baseband processor protocol) |

| UART              | Universal Asynchronous Receiver Transmitter                                                                           |

| UFS               | Universal Flash Storage                                                                                               |

| UIM               | User Identity module                                                                                                  |

| USB               | Universal Serial Bus                                                                                                  |

| USB HS            | USB High Speed                                                                                                        |

| USB SS            | USB Super Speed                                                                                                       |

# 3 Snapdragon 845 Hardware Development Kit

#### 3.1 Introduction

The Snapdragon 845 Hardware Development Kit provides a quick reference or evaluation platform for Qualcomm's Snapdragon 845 processor. This kit is suited for Android / Linux application developers, OEMs, consumer manufacturers, hardware component vendors, video surveillance, robotics, camera vendors, and flash chip vendors to evaluate, optimize, test and deploy applications that can utilize the Qualcomm® Snapdragon™ 845 technology.

#### 3.2 Development Platform Notice

This development platform contains RF/digital hardware and software intended for engineering development, engineering evaluation, or demonstration purposes only and is meant for use in a controlled environment. This device is not being placed on the market, leased or sold for use in a residential environment or for use by the general public as an end user device.

This development platform is not intended to meet the requirements of a commercially available consumer device including those requirements specified in the European Union directives applicable for Radio devices being placed on the market, FCC equipment authorization rules or other regulations pertaining to consumer devices being placed on the market for use by the general public.

This development platform may only be used in a controlled user environment where operators have obtained the necessary regulatory approvals for experimentation using a radio device and have appropriate technical training. The device may not be used by members of the general population or other individuals that have not been instructed on methods for conducting controlled experiments and taking necessary precautions for preventing harmful interference and minimizing RF exposure risks. Additional RF exposure information can be found on the FCC website at <a href="http://www.fcc.gov/oet/rfsafety/">http://www.fcc.gov/oet/rfsafety/</a>

## 3.3 Anti-Static Handling Procedures

The Snapdragon 845 Hardware Development Kit has exposed electronics and chipsets. Proper anti-static precautions should be employed when handling the kit, including but not limited to:

- Using a grounded anti-static mat

- Using a grounded wrist or foot strap

#### 3.4 Kit Contents

The Snapdragon 845 Hardware Development Kit includes the following:

- Snapdragon 845 processor board with the Snapdragon<sup>™</sup> 845 (SDA845) processor main CPU board

- Mini-ITX form-factor carrier board for I/O and connecting with external peripherals

- 12V power adapter

- o USB type-C cable and charger

- o 5.7" (1440x2560) TFT Display card (Additional Accessory)

- Lithium ion battery 4.4V/3000mAh

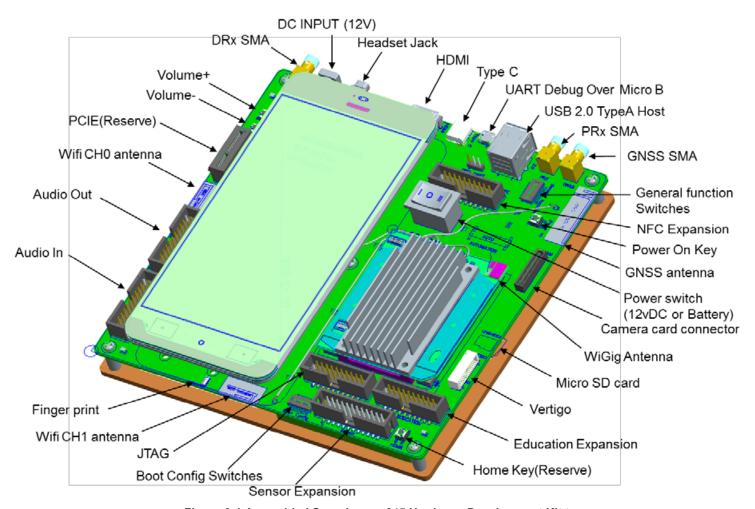

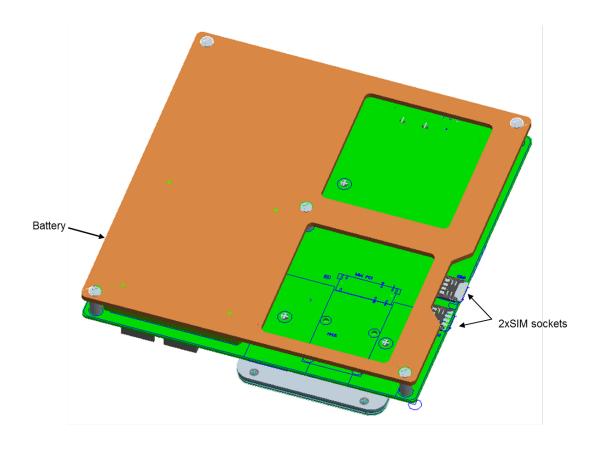

Figure 3-1 Assembled Snapdragon 845 Hardware Development Kit top

Figure 3-2 Assembled Snapdragon 845 Hardware Development Kit bottom

The development kit comes with Android software pre-programmed on the CPU board or processor board. Contact Lantronix for availability of camera modules, sensor boards, and other accessories: sales@lantronix.com

#### 3.5 Hardware Identification Label

Labels are present on the processor board. The following information is conveyed:

- Serial Number

- WIFI MAC address

Refer to <a href="http://tech.intrinsyc.com/projects/serialnumber/wiki">http://tech.intrinsyc.com/projects/serialnumber/wiki</a> for more details about locating the serial number, as this will be needed to register the development kit. To register a development kit, visit: <a href="https://tech.intrinsyc.com/account/register">https://tech.intrinsyc.com/account/register</a>.

Note: keep the serial number for warranty purposes.

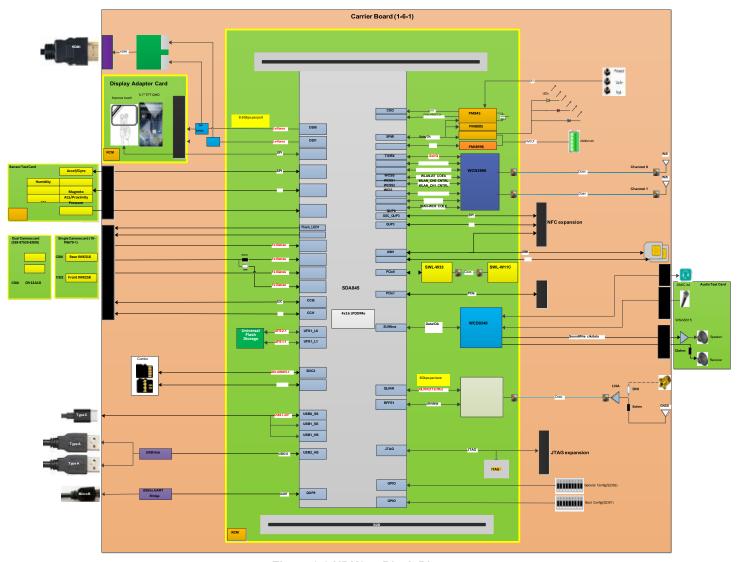

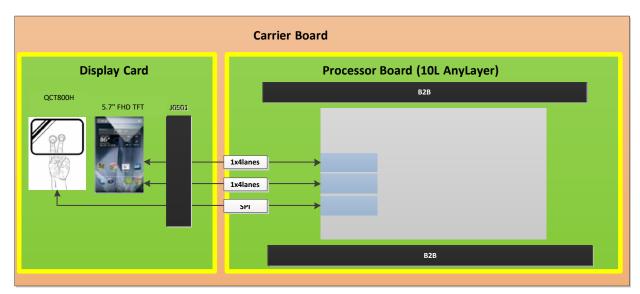

# 3.6 System Block Diagram

The following diagram explains the interconnectivity and peripherals on the development kit.

Figure 3-3 HDK845 Block Diagram

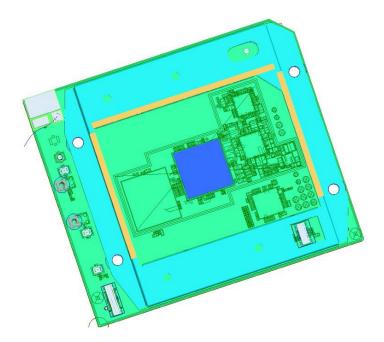

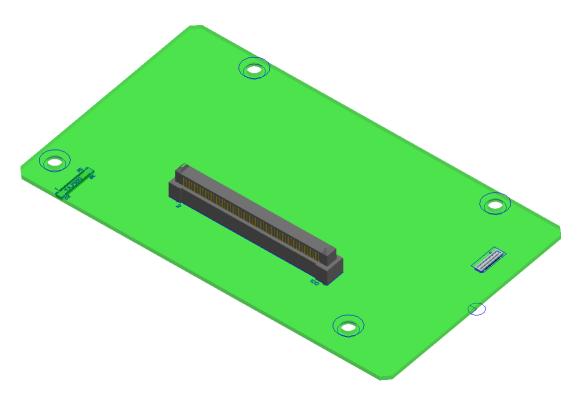

# **4 Processor Board**

The CPU or processor board provides the basic common set of features with minimal integration efforts for end users. It contains the followings:

- Snapdragon<sup>TM</sup> 845 (SDA845) main application processor

- Memory: 128GB UFS 2.1 + LPDDR4x (PoP) up to 1866MHz 6GB RAM

- PMIC: PM845 + PM8005 + PMI8998

- SMB1355 Parallel charger

- WCN3990 Atheros Wi-Fi + BT +FM combo chip over SLIMbus, Analog IQ, UART, PCM

- WCD9340 Audio Code

- SDR845 GNSS support

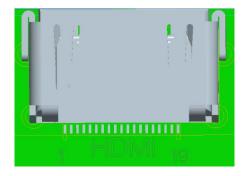

Figure 4-1 HDK Processor Board

The HDK845 processor board is where all the processing occurs. It is connected to the carrier board via two 240-pin high speed board-to-board connector. The purpose of the connectors is to bring out essential signals such that other peripherals can interface with the platform.

# **4.1 Processor Board Mechanical Properties**

Table 4-1 HDK845 Processor Board Mechanical Properties

| Dimension                                                                                            | 42 cm <sup>2</sup> (60 mm x 70 mm)              |  |  |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------|--|--|

| Interface                                                                                            | two 240-pin high speed board-to-board connector |  |  |

| Thermal A top side heat sink and a bottom side heat conductive metal plate are installed by default. |                                                 |  |  |

# 4.2 Hardware Specification

Table 4-2 HDK845 Hardware Features

| Subsystem /<br>Connectors | Feature Set | Description                                        | Specification                                                                                             |

|---------------------------|-------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| Chipset                   | SDA845      | Qualcomm® 845 Snapdragon <sup>™</sup><br>Processor | 64-bit applications<br>processor (Kryo 385) with<br>2 MB L3 cache                                         |

|                           |             |                                                    | Quad high-performance<br>Kryo cores targeting up to                                                       |

|                           |             |                                                    | 2.6 GHz – Gold cluster<br>with 256 kB L2 cache per<br>core                                                |

|                           |             |                                                    | Quad low-power Kryo<br>cores targeting up to 1.7<br>GHz – Silver cluster with<br>128 kB L2 cache per core |

| Subsystem /<br>Connectors | Feature Set                                                 | Description                                            | Specification                                                                                                                                   |

|---------------------------|-------------------------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | PMIC (PM845, PM8005<br>&PMI8998)                            | Qualcomm® PMIC, Companion<br>PMIC for SDA845 processor | PM845 Primary core<br>PMIC. PON, POFF, and<br>reset master. Generates<br>system clocking and<br>tightly coupled chipset<br>power.               |

|                           |                                                             |                                                        | PM8005 Secondary core PMIC. Delivers tightly coupled chipset power from opposite side of the MSM™ device to optimize power corridors on the PCB |

|                           |                                                             |                                                        | PMI8998 the interface<br>PMIC. Most of the input<br>power management<br>functions (including<br>charger) and user<br>interfaces                 |

| Memory                    | LPDDR4x                                                     | 6GB LPDDR4X                                            | LPDDR4x up to 1866MHz                                                                                                                           |

|                           | UFS                                                         | 128GB UFS2.1                                           | UFS 2.1                                                                                                                                         |

| Connectivity              | Wi-Fi 2.4 GHz/ 5GHz via<br>WCN3990 – Analog IQ, WSI<br>2.0, | Wi-Fi Atheros WCN3990Wi-Fi +<br>BT<br>+FM Combo Chip   | 802.11a/b/g/n/ac 2.4/5.0<br>GHz via WCN3990 over<br>analog IQ, WSI 2.0,                                                                         |

|                           | BT 2.4 GHz via WCN3990                                      | Wi-Fi Atheros WCN3990                                  | Support BT 5.0 + HS and                                                                                                                         |

|                           | - UART / SLIMbus                                            | Wi-Fi + BT +FM Combo Chip                              | backward compatible with BT 1.x, 2.x + EDR                                                                                                      |

|                           | GNSS via SDR845 –Qlink<br>Qualcomm Proprietary<br>Protocol  | GNSS Frontend                                          | GPS/ GLONASS/ COMPASS/Galileo                                                                                                                   |

|                           | WiGig via SWL-W33 – PCle<br>Gen2                            | SWL-W33 BB/MAC and SWL-<br>W11C                        | 802.11ad-60 GHz                                                                                                                                 |

|                           |                                                             | RF based SiP modules                                   |                                                                                                                                                 |

| RF                        | 2xWLAN / BT                                                 | Connect to antenna on carrier board via coax cable     | 2.4/ 5 GHz                                                                                                                                      |

|                           | 1x GNSS                                                     | Connect to antenna on carrier board via coax cable     | GPS/ GLONASS/ COMPASS /Galileo                                                                                                                  |

| Subsystem /<br>Connectors | Feature Set                                                    | Description                                              | Specification                                                                                      |

|---------------------------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|                           | 1x WiGig                                                       | Connect to antenna on processor board via coax cable     | 802.11ad-60 GHz                                                                                    |

| Audio                     | 1 x Headset Output                                             | Headset/ headphone output                                | Analog differential output                                                                         |

|                           | 2 x Loud-speaker                                               | 2 x loud-speaker output                                  | Digital output                                                                                     |

|                           | 1 x Earpiece output                                            | Earpiece output                                          | Analog differential output                                                                         |

|                           | 3 x analog MICs                                                | Analog MIC input                                         | Analog differential input                                                                          |

|                           | 4 x digital MICs                                               | Digital MIC input                                        | Digital input                                                                                      |

| Camera                    | 4 x MIPI CSI                                                   | 1x 120pin Camera Connector for CSI0, CSI1, CSI2 and CSI3 | MIPI Allie Specification v1.2                                                                      |

| Display                   | 2 x MIPI DSI (DSI0 & DSI1)  + Touch  100-pin display Connector | 100- pin display connector                               | MIPI Allie Specification<br>v1.2.  MIPI D-PHY Specification<br>v0.65, v0.81, v0.90, v1.01<br>,v1.2 |

| USB                       | 2 x Type-A USB 2.0 HOST<br>1 x Type-C USB 3.1                  | Type-A USB 2.0 HOST Type-C<br>USB 3.1                    | USB2.0 Hub USB3.1                                                                                  |

| PCle                      | 2 x PCIe                                                       | PCIe0 for WiGig module PCIe1 for PCIe 1X Slot (Reserve)  | PCIE0 is a Gen2 1-lane interface.  PCIE1 is a Gen3 1-lane interface.                               |

| Connectors                | 2 x 240pin processor board connector                           | Connector for Processor board                            | 2 x 240 pin B2B connector                                                                          |

# **5 Carrier Board**

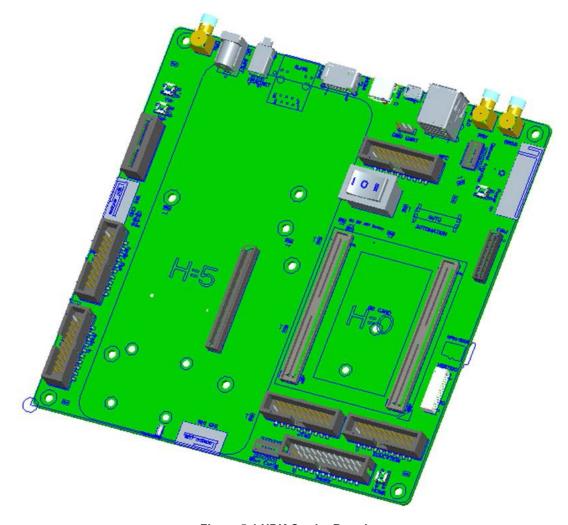

The HDK845 Carrier board is a Mini-ITX form factor board with various connectors used for connecting different peripherals. The following are the mechanical properties of the carrier board:

Table 5-1 HDK845 Carrier Board Mechanical Properties

| Dimension        | 289 cm <sup>2</sup> (170mm x 170mm)                                                 |

|------------------|-------------------------------------------------------------------------------------|

| Form Factor      | Mini-ITX                                                                            |

| Major Interfaces | Processor Board: 2x240 pin board to board connector Display: 100 pin board to board |

| Thermal          | Thermal pad is placed between the Processor board and carrier board                 |

Figure 5-1 HDK Carrier Board

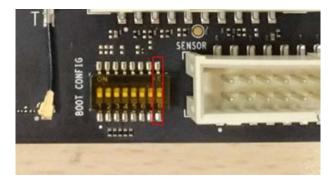

# **5.1 Dip switch Configuration Options**

There is one DIP switch S2301 on the south top side of the HDK845 carrier board. The 8-bit switch allows the user to control the system configuration and boot options. Table below outlines

Table 5-2 Dip Switch S2301 HW / SW Configuration

| Function             | DIP Switch | Description                                                                                      | Notes                                                                                                                                                                                                                             |

|----------------------|------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FORCED_USB_BOOT      | S2301-1    | Toggles between FORCE<br>USB boot and EDL mode.<br>Enables FOCE USB<br>(GPIO 57) when DIP        | Default out of the box configuration is OFF                                                                                                                                                                                       |

| WATCHDOG _DISABLE    | S2301-2    | Enables WATCHDOG_DISABLE when DIP switch turned on. Controlled by SDA- GPIO 101                  | Default out of the box configuration is OFF                                                                                                                                                                                       |

| BOOT_CONFIG[1]       | S2301-3    | Enables SDA boot configuration 1 when DIP switch turned on.  Controlled by SDA-GPIO 99           | Default out of the box configuration is OFF                                                                                                                                                                                       |

| BOOT_CONFIG[2]       | S2301-4    | Enables SDA boot configuration 2 when DIP switch turned on.  Controlled by SDA-GPIO100           | Default out of the box configuration is OFF                                                                                                                                                                                       |

| BOOT_CONFIG[3]       | S2301-5    | Enables SDA boot configuration 3 when DIP switch turned on.  Controlled by SDA GPIO133           | Default out of the box configuration is OFF                                                                                                                                                                                       |

| N/C                  | S2301-6    | NA                                                                                               | NA                                                                                                                                                                                                                                |

| DSI0_SW_SEL(Reserve) | S2301-7    | Select DSI0 data path<br>between display card and<br>HDMI  Default route DSI0 to<br>display card | Default out of the box configuration is OFF This DIP is default disabled.  DSI0 data path is default simultaneously controlled by S2301-8.  To separately control DSI0 path with this DIP needs HW change (DNI R3404, SMT R3403). |

| Function    | DIP Switch | Description                                                                                   | Notes                                                              |

|-------------|------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| DSI1_SW_SEL | S2301-8    | Select DSI1 data path<br>between display and<br>HDMI<br>Default route DSI1 to<br>display card | Default out of the box configuration is OFF DSI1 will be routed to |

There is another DIP switch S2302 on the north top side of HDK845 carrier board. The 8-bit switch allows the user to control the system configuration and boot options.

Table 5-3 Dip Switch S2302 HW / SW configuration

| Function       | DIP Switch | Description                                                                          | Notes                                                                                   |

|----------------|------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| CHARGE_DISABLE | S2302-1    | Disable charge when DIP switch turned on                                             | Default out of the box configuration is OFF which enables system charge from USB        |

|                |            |                                                                                      | Note: make sure turn on<br>this switch when DC-12V<br>input and USB are both<br>present |

| N/C            | S2302-2    | NA                                                                                   | Not used in HDK845                                                                      |

| HUB_RESET_SW   | S2302-3    | Enables hardware reset<br>from general<br>switch(J2204) when DIP<br>switch turned on | Default out of the box configuration is OFF Note: Default HUB reset                     |

|                |            |                                                                                      | control is from s/w,                                                                    |

|                |            |                                                                                      | hardware rework is<br>needed to enable this<br>function                                 |

| MSM_PS_HOLD    | S2302-4    | Enables the JTAG_PS_HOLD mode when DIP switch turned on                              | Default out of the box configuration is OFF                                             |

| AMOLED_LCD_SEL | S2302-5    | Select power supplier configuration between AMOLED and LCD                           | Default out of the box configuration is OFF                                             |

|                |            |                                                                                      | Note: LCD type display panel is supported by default                                    |

| QUP0_SPI_SEL   | S2302-6    | Select QUP0 path<br>between NFC(J2401) and<br>Education(J2801)                       | Default out of the box configuration is OFF <b>Note:</b> QUP0 is default                |

| QUP15_SPI_SEL  | S2302-7    | Select QUP15 path<br>between display card<br>(J1301) and onboard                     | Default out of the box configuration is OFF.                                            |

|                |            | fingerprint(J3102)                                                                   | Note: QUP15 is default routed to onboard fingerprint                                    |

| Function      | DIP Switch | Description                            | Notes                                                                |

|---------------|------------|----------------------------------------|----------------------------------------------------------------------|

| QUP_TP_CONFIG | S2302-8    | Config the signals connected to QUP_TP | Default out of the box configuration is OFF Note: SSC SPI2 is routed |

**WARNING**: Before making any changes to the dip switch, make sure to note down the previous configuration.

# **5.2 HDK845 Carrier Board Expansion Connectors**

The table below lists the connectors, expansions and their usages on the carrier board:

Table 5-4 Carrier Board Expansion options and their usage

| Domain               | Description                                             | Specification                                                  | Usage                                                                        |

|----------------------|---------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|

| Power                | AC / Barrel charger                                     | 12 V DC Power Supply<br>5 A                                    | Power Supply                                                                 |

|                      | Battery connector                                       | 8 pin header                                                   | For providing power from 4.4V/2850mAh battery                                |

| Debug Serial via USB | Debug Serial UART console over USB for development      | USB Micro B connector                                          | Development Serial<br>Connector for debug output<br>via USB                  |

| JTAG                 | OS / Firmware /QFROM<br>Programming / Debugging<br>JTAG | Standard 20-pin connector,<br>ARM and Open DSP –<br>Lauterbach | QFROM / eMMC / Platform<br>EEPROM programming<br>ARM / Open DSP<br>debugging |

| Buttons              | Power                                                   | SMD Button                                                     | Power Button for Suspend /<br>Resume and Power off                           |

|                      | Volume +                                                | SMD Button                                                     | Volume +Key                                                                  |

|                      | Volume –                                                | SMD Button                                                     | Volume – Key                                                                 |

|                      | Home                                                    | SMD Button                                                     | Reserved button for Home or general purpose                                  |

| NFC Board Header     | NFC Board Header 20 pin NFC expansion connectors        |                                                                | NA                                                                           |

| UFS/Micro SD Combo   | UFS/Micro SD card                                       | UFS card/4bit Micro SD card support                            | External Storage                                                             |

| Audio Jack           | Audio Jack Supported by WCD9340                         | Nomal Open, support US<br>Standard CTIA headset by<br>default  | Audio headset support                                                        |

| Domain                                                      | Description                             | Specification                                                                                                                                 | Usage                                                                                                                    |

|-------------------------------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 3-Digital Microphone via<br>audio input expansion<br>header | Audio expansion<br>Supported by WCD9340 | Digital Audio header                                                                                                                          | For Digital audio input for Digital MIC, I2S codec, Slim bus interface.                                                  |

| 3-Analog Microphone via<br>audio input expansion<br>header  | Audio expansion<br>Supported by WCD9340 | Analog Audio header                                                                                                                           | For Analog audio input for<br>Analog MIC (differential<br>signal)                                                        |

| 2-Loud Speaker via audio output expansion header            | Audio expansion<br>Supported by WCD9340 | Analog Audio header                                                                                                                           | For loud speaker output after signal has been processed                                                                  |

| Earpiece via audio output expansion header                  | Audio expansion<br>Supported by WCD9340 | Analog Audio header                                                                                                                           | For earpiece output after signal has been processed                                                                      |

|                                                             | PCle1 for PCle 1X Slot<br>(Reserve)     | Gen3 1-lane interface.                                                                                                                        | General-purpose<br>peripherals, such as Gigabit<br>Ethernet, Gigabit Wi-Fi, or<br>PCIe based audio / video<br>processors |

| USB 2.0 Host                                                | USB 2.0 Host                            | Type-A dual port header                                                                                                                       | For Mouse and Keyboard                                                                                                   |

| USB 3.1                                                     | USB 3.1                                 | Type-C header                                                                                                                                 | Transfer data to and from CPU                                                                                            |

| WLAN Antenna                                                | 2X PCB Antenna                          | 2.4 – 5 GHz                                                                                                                                   | Antenna to Processor board                                                                                               |

| Domain                                                      | Description                             | Specification                                                                                                                                 | Usage                                                                                                                    |

| GNSS Antenna                                                | PCB Antenna                             | GPS:  1574.42 MHz – 1576.42 MHz  GLONASS:  1587 MHz – 1606 MHz  COMPASS: 1559.05 to 1563.14MHz  Galileo: 4.092MHz BW (centered on 1575.42MHz) | Antenna to Processor board                                                                                               |

| LED                                                         | 3xLED                                   | Red: PMIC Driven  Green: PMIC Driven  Blue: PMIC Driven                                                                                       | Red: General purpose  Green: General purpose  Blue: General purpose                                                      |

| Domain                          | Description                                            | Specification                                                                           | Usage                                                                   |

|---------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| LCD Display and Touch connector | 100 pin for LCD signals from<br>B2B boards for display | 4-lane MIPI DSI0 , DSI1<br>I2C/SPI/GPIO<br>Backlight                                    | Can work as one dual DSI or both independent display                    |

|                                 |                                                        | MIPI Allie Specification v1.2<br>MIPI D-PHY Specification<br>v0.65,v0.81, v0.90, v1.01, |                                                                         |

|                                 |                                                        | V1.2                                                                                    |                                                                         |

|                                 |                                                        | MIPI C-PHY Specification v1.0                                                           |                                                                         |

| Sensor header                   | 24 pin sensor header                                   | 24 pin sensor header                                                                    | Header to connect sensor board.                                         |

| SIM Card                        | WWAN SIM card connector (optional)                     | 2x 4bit Micro SIM card support                                                          | For WWAN mini PCI express cards (for internal use only – not supported) |

| CSI Camera connectors           | 1 x 120pin connector with<br>MCLK, GPIOS, CCI          | Supports CSI0, CSI1 and<br>CSI2 via one 120pin<br>connector                             | Single Rear, Front camera  Dual Camera                                  |

|                                 | 1 x 120pin connector with MCLK, GPIOS, CCI             | 3 x MIPI-CSI each 4 lane                                                                | Iris Camera                                                             |

|                                 |                                                        | External flash driver control                                                           |                                                                         |

|                                 |                                                        | Support for 3D camera configuration                                                     |                                                                         |

|                                 |                                                        | Separate MCLK / CCI control                                                             |                                                                         |

|                                 |                                                        | Supports CSI3 via one 23pin connector on Processor board                                |                                                                         |

|                                 |                                                        | 1 x MIPI-CSI 2 lane                                                                     |                                                                         |

|                                 |                                                        | Separate MCLK / CCI control                                                             |                                                                         |

|                                 |                                                        | MIPI Allie Specification v1.2<br>for Camera Serial Interface                            |                                                                         |

The following sections will provide in depth information on each expansion headers and connectors on the carrier board. The information listed below is of particular use for those who want to interface other external hardware devices with the HDK845. **Before connecting anything to the development kit, ensure the device meets the specific hardware requirements of the processor.**

#### 5.2.1 Power Option

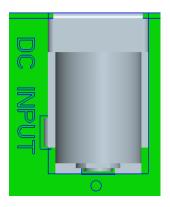

The HDK development kit power source connects to the 12V DC power supply jack J0701. Starting from the power jack, the 12V power supply branches off into different voltage rails via step down converters on the carrier board and PMIC on the Processor board. The processor board is powered by 3.9V via Silergy step down converter U0703 on the carrier board.

Figure 5-2 J0701 12V DC Power Jack

The processor board includes three PMIC modules. The functionalities of the three modules are outlined below.

PM845 and PM8005 core PMICs are used for:

- Source various regulated power rails

- Source system clock

PMI8998 Interface PMIC is used for:

- Source various regulated power rails

- Support for battery charging on the PM845 is configurable on the platform. The carrier board uses a 3.9V constant power input and battery to the processor board. A DIP switch is used to enable/disable charge function. Make sure turn off battery charging when 12V DC in is used and USB charger is inserted.

#### 5.2.2 Debug Serial UART header J2103

Figure 5-3 J2103 3.3V TTL Debug UART

The header consists of TX, RX and GND pins. It is a 3.3V TTL UART header. To get the serial terminal working with a PC, the following cable (or similar) is needed

http://www.digikey.ca/product-detail/en/TTL-232R-RPI/768-1204-ND/4382044

Table 5-5 Debug UART Header J2103 Pin-out

| Description         | Signal       | pin      | FTDI RPI cable connection |

|---------------------|--------------|----------|---------------------------|

| SDA UART RX (GPIO5) | QUP9_UART_RX | J2103[1] | Orange                    |

| SDA UART TX (GPIO4) | QUP9_UART_TX | J2103[2] | Yellow                    |

| GND                 | GND          | J2103[3] | Black                     |

### 5.2.3 Debug Serial UART over USB J2102

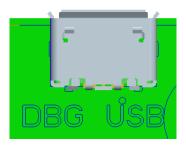

Figure 5-4 J2102 Debug UART over USB

The UART connection used on the HDK845 is a USB micro B connector (J2102). This debug UART is available over USB via the FTDI FT232RQ chip on the carrier board. To get the serial terminal working with a PC, user needs to ensure that the appropriate FTDI drivers are installed.

#### 5.2.4 JTAG header J2101

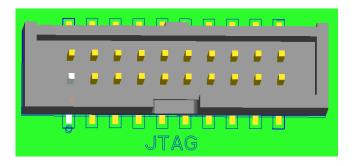

Figure 5-5 J2101 JTAG header

This connector provides a JTAG interface to the main processor by which users can connect a JTAG (Lauterbach / USB Wiggler) 20 pin ARM JTAG.

NOTE: It does not provide software support for JTAG

Table 5-6 JTAG Header J2101 Pin out

| Description                   | Signal | Pin NO    | Description                        | Signal    | Pin NO    |

|-------------------------------|--------|-----------|------------------------------------|-----------|-----------|

| GND                           | GND    | J2101[2]  | JTAG Power detect                  | JTAG_PWR  | J2101[1]  |

| GND                           | GND    | J2101[4]  | Target<br>RESET_N<br>signal        | TRST_N    | J2101[3]  |

| GND                           | GND    | J2101[6]  | TDI Signal<br>(Target DATA<br>IN)  | TDI       | J2101[5]  |

| GND                           | GND    | J2101[8]  | TMS Signal                         | TMS       | J2101[7]  |

| GND                           | GND    | J2101[10] | TCK Signal                         | TCK       | J2101[9]  |

| GND                           | GND    | J2101[12] | JTAG_RTCK signal                   | JTAG_RTCK | J2101[11] |

| GND                           | GND    | J2101[14] | TDO Signal<br>(Target Data<br>Out) | TDO       | J2101[13] |

| GND via<br>4.7KΩ pull<br>down | GND    | J2101[16] | Source<br>RESET_N<br>signal        | SRST_N    | J2101[15] |

| GND                           | GND    | J2101[18] | NC                                 | NC        | J2101[17] |

| JTAG detect N<br>signal       | DET_N  | J2101[20] | GND via<br>4.7KΩ pull<br>down      | GND       | J2101[19] |

### 5.2.5 Sensor IO Expansion Header J2501

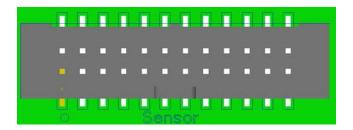

Figure 5-6 J2501 Sensor Expansion Header

The sensor expansion header J2501 allows for a 24-pin connection to an optional sensor board. If user application does not require a sensor, then this header can be used for other applications that require I2C or GPIO input and output connections.

Table 5-7 Sensor Expansion Header J2501 Pin out

| Description                                 | Signal           | Pin NO    | Description                                                      | Signal           | Pin NO    |

|---------------------------------------------|------------------|-----------|------------------------------------------------------------------|------------------|-----------|

| SSC I2C1                                    | SSC_I2C1_SD A    | J2501[1]  | Accelerometer interrupt input to processor via GPIO117           | ACCEL_INT        | J2501[2]  |

| SSC I2C1                                    | SSC_I2C1_SC L    | J2501[3]  | Cap interrupt<br>input to processor<br>via GPIO123               |                  | J2501[4]  |

| signal from                                 | MEMS_RESE<br>T_N | J2501[5]  | Gyroscope<br>interrupt input to<br>processor via<br>GPIO118      | GYRO_INT         | J2501[6]  |

| Sensor IO<br>PWR 1.8 V<br>VREG_LVS2<br>A    | SENS_IO_PW R     |           | •                                                                | SENS_ANA_P<br>WR | J2501[8]  |

| GND                                         | GND              | J2501[9]  | GND                                                              | GND              | J2501[10] |

| HRM<br>interrupt/<br>configurable<br>GPIO73 | HRM_INT          | J2501[11] | Touch screen<br>interrupt input<br>from processor<br>via GPIO125 | TS_INT_N         | J2501[12] |

| Description                    | Signal             | Pin NO    | Description                                                       | Signal             | Pin NO    |

|--------------------------------|--------------------|-----------|-------------------------------------------------------------------|--------------------|-----------|

| SSC SPI-1<br>chip select 2     | SSC_SPI1_CS<br>1_N | J2501[13] | Alternate sensor interrupt input to processor via GPIO120         | ALSP_INT_N         | J2501[14] |

| MISC GPIO<br>for<br>sensor via | SDA_GPIO62         | J2501[15] | Digital Compass<br>interrupt input to<br>processor via<br>GPIO119 | MAG_DRDY_I<br>NT   | J2501[16] |

| NC                             | NC                 | J2501[17] | Hall sensor<br>interrupt input to<br>processor via<br>GPIO124     | HALL_INT_N         | J2501[18] |

| SSC SPI-1<br>chip select 1     | SSC_SPI1_CS<br>0_N | J2501[19] | SSC SPI-1<br>data master out/<br>slave in                         | SSC_SPI_1_M<br>OSI | J2501[20] |

| SSC SPI-1<br>clock             | SSC_SPI1_CL K      | J2501[21] | SSC SPI-1<br>data master in/<br>slave out                         | SSC_SPI_1_M<br>ISO | J2501[22] |

| NC                             | NC                 | J2501[23] | SSC SPI-1<br>chip select 3                                        | SSC_SPI1_CS<br>2_N | J2501[24] |

In summary, if sensor application is not needed, this expansion header can provide SSC SPI1 and I2C. Refer to the schematic for more details and consider the power before connecting anything to this header.

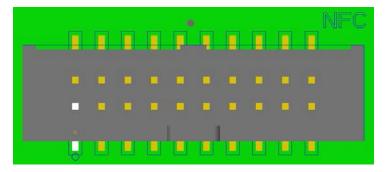

#### 5.2.6 NFC Expansion Header J2401

Figure 5-7 J2401 NFC Expansion Header

The NFC expansion header provides a 20-pin connector for attaching an optional NFC board This header also allows user to connect to the free GPIOs and I2C lines when NFC is not used; therefore, enabling other use cases. Refer to the table below for detailed information regarding the signals that are being brought out by this connector.

Table 5-8 NFC Expansion Header J2401 pin out

| Description                                                | Signal              | Pin NO    | Description                                  | Signal              | Pin NO    |

|------------------------------------------------------------|---------------------|-----------|----------------------------------------------|---------------------|-----------|

| QUP0                                                       | NFC_SPI_CLK         | J2401[1]  | QUP0                                         | NFC_SPI_MIS<br>O    | J2401[2]  |

| NFC power<br>request via<br>GPIO116                        | NFC_ESE_PW<br>R_REQ | J2401[3]  | SIM present<br>GPIO via SDA<br>GPIO112       | UMI1_DET_N          | J2401[4]  |

| SIM Card DATA line (UIM1) via                              | UIM1_DATA           | J2401[5]  | 3.9V<br>PROCESSOR<br>BOARD                   | VPH_PWR             | J2401[6]  |

| SIM Card Reset<br>line (UIM1) via<br>SDA GPIO111           | UIM1_RESET          | J2401[7]  | NFC interrupt IRQ<br>pin via SDA<br>GPIO63   | NFC_IRQ             | J2401[8]  |

| SIM CLK line<br>(SIM1) via SDA<br>GPIO110                  | UIM1_CLK            | J2401[9]  | NFC Disable<br>signal via SDA<br>GPIO12      | NFC_ENABLE          | J2401[10] |

| 1.8V Voltage<br>regulator supply<br>max 150mA via<br>PM845 | VREG_L9A_1<br>P8    | J2401[11] | QUP3 I2C SDA<br>line                         | NFC_I2C3_SD<br>A    | J2401[12] |

| 1.8V Voltage<br>regulator supply<br>via PM845              | VREG_S4A_1<br>P8    | J2401[13] | QUP3 I2C CLK                                 | NFC_I2C3_SC<br>L    | J2401[14] |

| GND                                                        | GND                 | J2401[15] | NFC clock<br>request signal via<br>PM GPIO21 | NFC_LNBBCL<br>K3_EN | J2401[16] |

| PM845 free<br>running clock via<br>buffer                  | LN_BB_CLK3_<br>NFC  | J2401[17] | NFC download<br>request via SDA<br>GPIO62    | NFC_DWL_RE<br>Q     | J2401[18] |

| QUP0<br>via SDA GPIO3                                      | NFC_SPI_CS_<br>N    | J2401[19] | QUP0<br>via SDA GPIO1                        | NFC_SPI_MO<br>SI    | J2401[20] |

In general, if there is no need for NFC application, this expansion header can provide two GPIOs, I2C, free running clocks, and enable voltage/ power source to external peripherals.

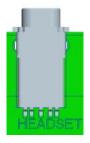

#### 5.2.7 Headset Jack J1501

Figure 5-8 Headphone Jack

The headset jack (J1501) is standard 3.5mm, Normal Open style. The hardware supports US Standard CTIA headset by default.

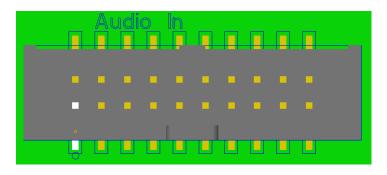

### 5.2.8 Audio Inputs Expansion Header J1601

Figure 5-9 J1601 Audio Inputs Expansion Header

This header expansion provides the following audio inputs:

- 3 digital mics

- 3 analog mics

- Voltage rails to support analog and digital mics

The table below outlines the pin out information of the audio inputs expansion header J1601:

Table 5-9 Audio Inputs Expansion Header J1601 Pin out

| Description                                      | Signal             | Pin NO    | Description                                      | Signal             | Pin NO    |

|--------------------------------------------------|--------------------|-----------|--------------------------------------------------|--------------------|-----------|

| Analog MIC1<br>positive<br>differential<br>input | CDC_IN1_P          | J1601[1]  | Analog MIC1<br>negative<br>differential<br>input | CDC_IN1_N          | J1601[2]  |

| Analog MIC2<br>positive<br>differential<br>input | CDC_IN3_P          | J1601[3]  | Analog<br>MIC2negative<br>differential<br>input  | CDC_IN3_N          | J1601[4]  |

| MIC bias<br>output voltage<br>1                  | MIC_BIAS1          | J1601[5]  | MIC bias<br>output voltage<br>3                  | MIC_BIAS3          | J1601[6]  |

| Analog MIC3<br>positive<br>differential<br>input | CDC_IN4_P          | J1601[7]  | Analog MIC3<br>negative<br>differential<br>input | CDC_IN4_N          | J1601[8]  |

| MIC bias<br>output voltage<br>4                  | MIC_BIAS4          | J1601[9]  | 3.3V power supply max 500mA                      | MB_VREG_3P         | J1601[10] |

| GND                                              | GND                | J1601[11] | GND                                              | GND                | J1601[12] |

| Clock for digital MIC3                           | CDC_DMIC_C<br>LK1  | J1601[13] | Clock for digital MIC1                           | CDC_DMIC_C<br>LK2  | J1601[14] |

| Digital<br>MIC3data line                         | CDC_DMIC_D<br>ATA1 | J1601[15] | Digital<br>MIC1data line                         | CDC_DMIC_D<br>ATA2 | J1601[16] |

| 1.8V power supply max 300mA                      | VREG_S4A_1<br>P8   | J1601[17] | Clock for digital MIC2                           | CDC_DMIC_C<br>LK3  | J1601[18] |

| GND                                              | GND                | J1601[19] | Digital<br>MIC2data line                         | CDC_DMIC_D<br>ATA3 | J1601[20] |

#### 5.2.9 Audio Outputs Expansion Header J1602

Figure 5-10 J1602 Audio Outputs Expansion Header

This header expansion provides the following audio outputs:

- 2 differential analog audio line out

- 2 single ended analog audio line out

- 1 differential analog earpiece amplifier output (no external amp needed)

- 2 speaker amplifiers enable control

- Voltage rails to support analog and digital mics

Table 5-10 Audio Outputs Expansion Header J1602 Pin out

| Description                                                               | Signal      | Pin NO   | Description                                                       | Signal          | Pin NO   |

|---------------------------------------------------------------------------|-------------|----------|-------------------------------------------------------------------|-----------------|----------|

| Analog audio<br>line out 1,<br>positive<br>differential<br>output         | LINE_OUT1_P | J1602[1] | Analog audio<br>line out 1,<br>negative<br>differential<br>output | LINE_OUT1_N     | J1602[2] |

| Analog audio<br>line out 2,<br>positive<br>differential<br>output         | LINE_OUT2_P | J1602[3] | Analog audio<br>line out 2,<br>negative<br>differential<br>output | LINE_OUT2_N     | J1602[4] |

| Audio line single<br>end outputs GND<br>reference (conn<br>ect to ground) | LINE_REF    | J1602[5] | 3.3V output power supply                                          | MB_VREG_3P<br>3 | J1602[6] |

| Analog audio<br>line out 1,<br>single ended<br>output                     | LINE_OUT1_P | J1602[7] | Analog audio<br>line out 2,<br>single ended<br>output             | LINE_OUT2_P     | J1602[8] |

| Description                                                            | Signal            | Pin NO    | Description                                                                | Signal           | Pin NO    |

|------------------------------------------------------------------------|-------------------|-----------|----------------------------------------------------------------------------|------------------|-----------|

| Analog earpiece amplifier out, positive differential output            | CDC_EAR_P         | J1602[9]  | Analog<br>earpiece<br>amplifier out,<br>negative<br>differential<br>output | CDC_EAR_M        | J1602[10] |

| GND                                                                    | GND               | J1602[11] | 3.8V output power supply                                                   | VPH_PWR          | J1602[12] |

| Digital sound<br>wire data for<br>WSA8810/<br>WSA8815<br>smart speaker | CDC_SWR_<br>C LK  | J1602[13] | Digital sound<br>wire data for<br>WSA8810/<br>WSA8815<br>smart speaker     | CDC_SWR_D<br>ATA | J1602[14] |

| amplifier                                                              |                   |           | amplifier                                                                  |                  |           |

| Speaker<br>amplifier<br>enable 1                                       | WSA_EN            | J1602[15] | Speaker<br>amplifier<br>enable 2                                           | SPKR_AMP_E<br>N2 | J1602[16] |

| 1.8V output power supply                                               | VREG_S4A_<br>1 P8 | J1602[17] | 12V output power supply                                                    | DC_IN_12V        | J1602[18] |

| 5.0V output power supply                                               | MB_VREG_5<br>P 0  | J1602[19] | GND                                                                        | GND              | J1602[20] |

#### **5.2.10 USB TYPE A Connector J1101**

Figure 5-11 J1101 USB2.0 Type A Connector

The on-board USB type A connector supports 2x USB 2.0 host interface.

#### 5.2.11 **USB3.1 Type C Connector J1201**

The on-board Type-C connector supports USB 3.1 Gen1, which also supports Type-C with DisplayPort V1.3

#### 5.2.12 On Board PCB WLAN Antenna

The HDK845 carrier board has two on-board PCB antennas that connects to the WCN3990 WiFi module on the processor board via coaxial cables that attaches to MH4L receptacles. These antennas connect to the processor board in the following configuration:

- WIFI CH0 on the carrier board connects to ANT0 on the WCN3990 WiFi module

- WIFI CH1 on the carrier board connects to ANT1 on the WCN3990 WiFi module

Figure 5-12 On Board PCB WLAN Antennas

#### 5.2.13 On Board PCB GNSS Antenna

Figure 5-13 GNSS On Board PCB GNSS Antennas

The HDK845 carrier board has one on-board PCB antennas on the bottom side that connects to the Processor board via coaxial cable that attaches to MH4L receptacles. The on-board antenna is connected to the Processor board by default, meanwhile, there are 0-ohm jumpers for user to use an external GNSS antenna via the SMA connector. The option pads are between the antenna and the eLNA input.

Table 5-11 GNSS Antenna Option

| Option        | R3804 | R3805 |

|---------------|-------|-------|

| On-Board      | DNI   | Stuff |

| SMA connector | Stuff | DNI   |

#### **5.2.14 GNSS SMA Connector J3802**

The GNSS SMA connector is reserved for an external antenna. Refer to Table 5-11 GNSS Antenna Option, stuff R3804 and remove R3805 to make the path active.

Figure 5-14 GNSS SMA Connector

#### 5.2.15 Camera connector

The HDK845 development kit supports three 4-lane MIPI camera interfaces via a 120pin connector, it also supports one 2-lane MIPI camera interface via a 23-pin connector on the Processor board.

The following are some features of the camera connectors:

- 3 x 4 lane MIPI CSI signals, CSI0, CSI1 and CSI2

- 1 x 2 lane MIPI CSI signals, CSI3 reserved on Processor board

- Support for 3D camera configuration

- □ Separate I2C control (CCI0, CCI1)

- Self-regulated camera modules can be powered with 3.3V power (MB\_VREG\_3P3)

- Uses Amphenol 11826-ACA connector for exposing MIPI, MCLK, CCI, GPIOs and Power rails.

- Use Amphenol 11828-1CA mating connector to access these signals.

Figure 5-15 Camera Connector (J1701)

| Pin# | Signal         | Description          | Pin# | Signal       | Description          |

|------|----------------|----------------------|------|--------------|----------------------|

| A1   | CAM_VREG_3P3   | 3.3V power supplier  | B1   | DGND         |                      |

| A2   | CAM_VREG_3P3   | 3.3V power supplier  | B2   | CCI_I2C_SDA0 | SDA GPIO17           |

| А3   | CAM_VREG_3P3   | 3.3V power supplier  | В3   | CCI_I2C_SCL0 | SDA GPIO18           |

| A4   | DGND           |                      | B4   | DGND         |                      |

| A5   | CAM_S5A        | 2.04V power supplier | B5   | CCI_I2C_SDA1 | SDA GPIO19           |

| A6   | P1V8_CAM_IOVDD | 1.8V power supplier  | В6   | CCI_I2C_SCL1 | SDA GPIO20           |

| A7   | DGND           |                      | В7   | DGND         |                      |

| A8   | FLASH_LED1     | FLASHLED1            | В8   | CAM_S3A      | 1.35V power supplier |

| A9   | FLASH_LED1     | FLASHLED1            | В9   | CAM_S3A      | 1.35V power supplier |

| A10  | DGND           |                      | B10  | DGND         |                      |

| Pin# | Signal            | Description | Pin# | Signal         | Description         |

|------|-------------------|-------------|------|----------------|---------------------|

| A11  | FLASH_LED2        | FLASHLED2   | B11  | CAM_ELDO4_EN   | PM845 GPIO9         |

| A12  | FLASH_LED2        | FLASHLED2   | B12  | CAM_ELDO1_EN   | PM845 GPIO12        |

| A13  | DGND              |             | B13  | DGND           |                     |

| A14  | FLASH_LED3        | FLASHLED3   | B14  | NC             |                     |

| A15  | FLASH_LED3        | FLASHLED3   | B15  | FLASH_R3LED_EN | PMI8998 GPIO3       |

| A16  | DGND              |             | B16  | DGND           |                     |

| A17  | MIPI_CSI2_LANE3_N | CSI2 data   | B17  | FLASH_FRONT_EN | SDA GPIO21          |

| A18  | MIPI_CSI2_LANE3_P | CSI2 data   | B18  | FL_STROBE_TRIG | SDA GPIO22          |

| A19  | DGND              |             | B19  | DGND           |                     |

| A20  | MIPI_CSI2_LANE2_N | CSI2 data   | B20  | P1V8_CAM_IOVDD | 1.8V power supplier |

| Pin# | Signal            | Description | Pin# | Signal            | Description          |

|------|-------------------|-------------|------|-------------------|----------------------|

| A21  | MIPI_CSI2_LANE2_P | CSI2 data   | B21  | P1V2_DVDD_CAM1_2  | 1.2V power supplier  |

| A22  | DGND              |             | B22  | DGND              |                      |

| A23  | MIPI_CSI2_LANE1_N | CSI2 data   | B23  | P2V85_AVDD_CAM1_2 | 2.85V power supplier |

| A24  | MIPI_CSI2_LANE1_P | CSI2 data   | B24  | P2V85_AVDD_CAM1_2 | 2.85V power supplier |

| A25  | DGND              |             | B25  | DGND              |                      |

| A26  | MIPI_CSI2_LANE0_N | CSI2 data   | B26  | P2V8_VCM_LASER_RF | 2.8V power supplier  |

| A27  | MIPI_CSI2_LANE0_P | CSI2 data   | B27  | P2V8_VCM_LASER_RF | 2.8V power supplier  |

| A28  | DGND              |             | B28  | DGND              |                      |

| A29  | MIPI_CSI2_CLK_N   | CSI2 clock  | B29  | P1V2_DVDD_CAM1_2  | 1.2V power supplier  |

| A30  | MIPI_CSI2_CLK_P   | CSI2 clock  | B30  | P1V2_DVDD_CAM1_2  | 1.2V power supplier  |

| Pin# | Signal        | Description | Pin# | Signal            | Description |

|------|---------------|-------------|------|-------------------|-------------|

| C1   | CAM_MCLK0_BUF | SDA GPIO13  | D1   | DGND              |             |

| C2   | CAM0_RSTN     | SDA GPIO80  | D2   | MIPI_CSIO_LANE3_N | CSI0 data   |

| С3   | CAM_ELDO9_EN  | SDA GPIO79  | D3   | MIPI_CSIO_LANE3_P | CSI0 data   |

| C4   | DGND          |             | D4   | DGND              |             |

| C5   | CAM1_RSTN     | SDA GPIO28  | D5   | MIPI_CSIO_LANE2_N | CSI0 data   |

| C6   | CAM_ELDO3_EN  | SDA GPIO27  | D6   | MIPI_CSIO_LANE2_P | CSI0 data   |

| C7   | CAM_MCLK1_BUF | SDA GPIO14  | D7   | DGND              |             |

| C8   | DGND          |             | D8   | MIPI_CSIO_LANE1_N | CSI0 data   |

| С9   | CAM2_RSTN     | SDA GPIO9   | D9   | MIPI_CSIO_LANE1_P | CSI0 data   |

| C10  | CAM_MCLK2_BUF | SDA GPIO15  | D10  | DGND              |             |

| C11  | CAM_ELDO2_EN  | SDA GPIO8   | D11  | MIPI_CSIO_LANEO_N | CSI0 data   |

| C12  | DGND          |             | D12  | MIPI_CSIO_LANEO_P | CSI0 data   |

| C13  | CAM_MCLK3_BUF | SDA GPIO16  | D13  | DGND              |             |

| C14  | CAM3_RSTN     | SDA GPIO23  | D14  | MIPI_CSIO_CLK_N   | CSI0 clock  |

| C15  | OIS_SYNC      | SDA GPIO25  | D15  | MIPI_CSIO_CLK_P   | CSI0 clock  |

| C16  | DGND          |             | D16  | DGND              |             |

| C17  | LASER_IRQ     | SDA GPIO26  | D17  | MIPI_CSI1_LANE3_N | CSI1 data   |

| C18  | LASER_CE      | SDA GPIO100 | D18  | MIPI_CSI1_LANE3_P | CSI1 data   |

| C19  | DGND          |             | D19  | DGND              |             |

| Pin# | Signal                | Description          | Pin# | Signal            | Description |

|------|-----------------------|----------------------|------|-------------------|-------------|

| C20  | P2V8_CAMA3            | NC                   | D20  | MIPI_CSI1_LANE2_N | CSI1 data   |

| C21  | P2V8_VCM_LASER_<br>RF | 2.8V power supplier  | D21  | MIPI_CSI1_LANE2_P | CSI1 data   |

| C22  | DGND                  |                      | D22  | DGND              |             |

| C23  | CAM_IRQ               | SDA GPIO24           | D23  | MIPI_CSI1_LANE1_N | CSI1 data   |

| C24  | NC                    |                      | D24  | MIPI_CSI1_LANE1_P | CSI1 data   |

| C25  | DGND                  |                      | D25  | DGND              |             |

| C26  | P2V85_CAM0_AVD<br>D   | 2.85V power supplier | D26  | MIPI_CSI1_LANE0_N | CSI1 data   |

| C27  | NC                    |                      | D27  | MIPI_CSI1_LANE0_P | CSI1 data   |

| C28  | DGND                  |                      | D28  | DGND              |             |

| C29  | P1V05_DVDD_CAM<br>0   | 1.05V power supplier | D29  | MIPI_CSI1_CLK_N   | CSI1 clock  |

| C30  | P1V05_DVDD_CAM<br>0   | 1.05V power supplier | D30  | MIPI_CSI1_CLK_P   | CSI1 clock  |

The table below shows the combinations of camera usage for different use cases.

Table 5-13 MIPI CSI Camera Use Cases

| CSI PHY            | Use case        | Comment                                        |

|--------------------|-----------------|------------------------------------------------|

| CSI0               | Up to 4 lane    | One Camera of 4 lane or                        |

|                    |                 | One camera of 3 lane                           |

|                    |                 | One Camera of 2 lane                           |

|                    |                 | One Camera of 1 lane                           |